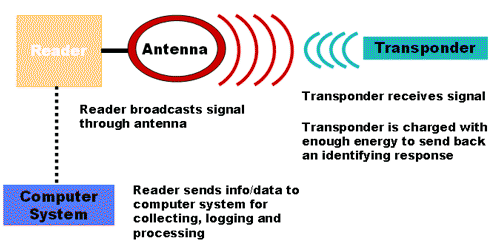

JTAG (مجموعة إجراء الاختبار المشترك) هي معيار IEEE 1149.1 راسخ تم تطويره في عام 1980 لحل مشكلات التصنيع التي حدثت داخل اللوحات الإلكترونية أو لوحات الدوائر المطبوعة . تُستخدم هذه التقنية لتوفير وصول اختبار كافٍ لكل لوحة معقدة عندما كان الوصول للاختبار يتناقص. وهكذا ، تم إطلاق تقنية مسح الحدود ومعيار JTAG أو مواصفات JTAG تم إنشاؤه. يتزايد تعقيد الإلكترونيات يومًا بعد يوم ، لذلك أصبحت مواصفات JTAG هي تنسيق الاختبار المقبول لاختبار الوحدات الإلكترونية المعقدة والمدمجة. تتناول هذه المقالة نظرة عامة على ملف JTAG بروتوكول - العمل مع التطبيقات.

ما هو JTAG؟

يُعرف الاسم الذي يتم إعطاؤه لمنفذ الوصول للاختبار القياسي IEEE 1149.1 بالإضافة إلى هندسة مسح الحدود باسم JTAG (مجموعة إجراءات الاختبار المشتركة). يتم استخدام بنية مسح الحدود هذه في الغالب داخل الكمبيوتر معالجات لأن أول معالج مع JTAG تم إصداره بواسطة Intel. يحدد معيار IEEE هذا ببساطة كيفية اختبار دوائر الكمبيوتر للتأكد مما إذا كان يعمل بشكل صحيح بعد إجراء التصنيع. على لوحات الدوائر ، يتم إجراء اختبارات للتحقق من وصلات اللحام.

توفر مجموعة عمل الاختبار المشترك عرضًا مفصلاً للمختبرين مع كل لوحة IC مما يساعد في تحديد أي أخطاء داخل لوحة الدائرة. بمجرد ربط هذا البروتوكول بشريحة ، يمكن لهذا أن يربط مسبارًا بالشريحة عن طريق السماح للمطور بالتحكم في الشريحة وكذلك اتصالاتها بالرقائق الأخرى. يمكن أيضًا للمطورين استخدام الواجهة مع مجموعة إجراءات الاختبار المشتركة لنسخ البرنامج الثابت إلى ذاكرة غير متطايرة في جهاز إلكتروني.

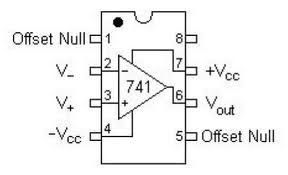

التكوين / الدبوس

تشتمل مجموعة إجراء الاختبار المشترك على 20 دبوسًا حيث تتم مناقشة كل دبوس ووظيفته أدناه.

Pin1 (VTref): هذا هو دبوس الجهد المرجعي المستهدف الذي يتم استخدامه للاتصال بمصدر الطاقة الرئيسي للهدف والذي يتراوح من 1.5 إلى 5.0VDC.

Pin2 (Vsupply): هذا هو جهد الإمداد المستهدف الذي يتم استخدامه لتوصيل مصدر الجهد الرئيسي للهدف 1.5VDC - 5.0VDC.

Pin3 (nTRST): هذا هو اختبار إعادة تعيين دبوس يستخدم لإعادة تعيين جهاز الحالة لوحدة تحكم TAP.

دبابيس (4 ، 6 ، 8 ، 10 ، 12 ، 14 ، 16 ، 18 ، 20): هذه دبابيس GND شائعة.

Pin5 (TDI): هذه بيانات الاختبار في الدبوس. يتم نقل هذه البيانات إلى الجهاز المستهدف. يجب سحب هذا الدبوس في حالة محددة على اللوحة الهدف.

Pin7 (TMS): هذا هو دبوس حالة وضع الاختبار الذي يتم سحبه لتحديد الحالة التالية لجهاز الحالة لوحدة تحكم TAP.

Pin9 (TCK): هذا هو دبوس ساعة الاختبار الذي يزامن عمليات آلة الحالة الداخلية في وحدة تحكم TAP.

Pin11 (RTCK): هذا هو دبوس Input Return TCK المستخدم في الأجهزة التي تدعم تسجيل الوقت التكيفي.

Pin13 (TDO): هذا هو دبوس إخراج بيانات الاختبار ، لذلك يتم نقل البيانات من الجهاز المستهدف إلى Flyswatter.

دبوس 15 (nSRST): هذا هو دبوس إعادة تعيين النظام المستهدف المتصل بإشارة إعادة الضبط الرئيسية للهدف.

الدبابيس 17 و 19 (NC): هذه ليست دبابيس متصلة.

JTAG العمل

الاستخدام الأصلي لـ JTAG هو اختبار الحدود. هنا ، لوحة دوائر مطبوعة بسيطة بما في ذلك اثنين من الدوائر المتكاملة مثل وحدة المعالجة المركزية & FPGA . قد تتضمن اللوحة النموذجية العديد من المرحلية. بشكل عام ، تشتمل الدوائر المتكاملة على العديد من المسامير المتصلة بشكل مشترك مع العديد من الوصلات. هنا ، في الرسم البياني التالي ، تظهر أربعة اتصالات فقط.

لذلك إذا قمت بتصميم العديد من اللوحات حيث كل لوحة بها آلاف الوصلات. في ذلك ، هناك بعض المجالس السيئة. لذلك نحن بحاجة إلى التحقق من اللوحة التي تعمل والتي لا تعمل. لذلك ، تم تصميم مجموعة عمل الاختبار المشترك.

يمكن لهذا البروتوكول استخدام دبابيس التحكم في جميع الرقائق ولكن في الرسم التخطيطي التالي ، ستقوم مجموعة عمل الاختبار المشترك بعمل جميع دبابيس إخراج وحدة المعالجة المركزية وجميع دبابيس الإدخال الخاصة بـ FPGA. بعد ذلك ، من خلال إرسال قدر من البيانات من دبابيس وحدة المعالجة المركزية وقراءة قيم المسامير من FPGA ، تنص JTAG على أن اتصالات لوحة PCB جيدة.

في الواقع ، تشتمل مجموعة عمل الاختبار المشترك على أربع إشارات منطقية TDI و TDO و TMS و TCK. وتحتاج هذه الإشارات إلى التوصيل بطريقة معينة. في البداية ، يتم توصيل TMS & TCK بالتوازي مع جميع الدوائر المتكاملة الخاصة بـ JTAG.

بعد ذلك ، يتم توصيل كل من TDI & TDO لتشكيل سلسلة. كما يمكنك أن تلاحظ ، يشتمل كل IC متوافق مع JTAG على 4 دبابيس يتم استخدامها لـ JTAG حيث تكون 3 دبابيس هي المدخلات ويتم إخراج الدبوس الرابع. الدبوس الخامس مثل TRST اختياري. عادةً ، لا تتم مشاركة دبابيس JTAG لأغراض أخرى.

باستخدام مجموعة إجراء الاختبار المشترك ، تستخدم جميع الدوائر المتكاملة اختبار الحدود الذي تم إنشاء السبب الأصلي بواسطة JTAG. في الوقت الحاضر ، تم تمديد استخدام هذا البروتوكول للسماح بأشياء مختلفة مثل تكوين FPGAs وبعد ذلك يتم استخدام JTAG في FPGA الأساسية لأغراض التصحيح.

هندسة JTAG

يتم عرض هندسة JTAG أدناه. في هذه البنية ، يتم مقاطعة جميع الإشارات الموجودة بين المنطق الأساسي للجهاز والدبابيس من خلال مسار مسح تسلسلي يسمى BSR أو Boundary Scan Register. يتضمن BSR هذا 'خلايا' مختلفة لمسح الحدود. بشكل عام ، لا تكون خلايا مسح الحدود هذه مرئية ولكن يمكن استخدامها لتعيين أو قراءة القيم في وضع الاختبار من دبابيس الجهاز.

تستخدم واجهة JTAG التي تسمى TAP أو Test Access Port إشارات مختلفة لدعم عملية مسح الحدود مثل TCK و TMS و TDI و TDO و TRST.

- تقوم إشارة TCK أو Test Clock ببساطة بمزامنة العمليات الداخلية لجهاز الحالة.

- يتم أخذ عينات من إشارة TMS أو Test Mode Select عند الحافة المتزايدة لإشارة ساعة الاختبار لتحديد الحالة التالية.

- تشير إشارة TDI أو Test Data In إلى البيانات المحولة إلى جهاز الاختبار ، وإلا فمنطق البرمجة. بمجرد أن تكون آلة الحالة الداخلية في الحالة الصحيحة ، يتم أخذ عينات منها عند الحافة المتزايدة لـ TCK.

- تشير إشارة TDO أو Test Data Out إلى البيانات المحولة لجهاز الاختبار ، وإلا فمنطق البرمجة. بمجرد أن تكون آلة الحالة الداخلية في الحالة الصحيحة ، فإنها تكون صالحة على الحافة المتناقصة لـ TCK

- TRST أو Test Reset هو دبوس اختياري يُستخدم لإعادة ضبط جهاز الحالة لوحدة التحكم TAP.

تحكم TAP

تتكون نقطة الوصول التجريبية في بنية JTAG من وحدة تحكم TAP ، وسجل التعليمات ، وسجلات بيانات الاختبار. تشتمل وحدة التحكم هذه على آلة حالة الاختبار المسؤولة عن قراءة إشارات TMS و TCK. هنا ، يتم استخدام دبوس i / p ببساطة لتحميل البيانات في الخلايا الحدودية بين دبابيس IC الأساسية والمادية ، وكذلك تحميل البيانات في أحد سجلات البيانات أو في سجل التعليمات. يتم استخدام دبوس o / p لقراءة البيانات من السجلات أو الخلايا الحدودية.

يتم التحكم في آلة الحالة الخاصة بجهاز التحكم TAP بواسطة TMS ويتم تسجيلها بواسطة TCK. تستخدم آلة الحالة مسارين للدلالة على وضعين مختلفين مثل وضع التعليمات ووضع البيانات.

السجلات

هناك نوعان من السجلات المتاحة داخل مسح الحدود. يتضمن كل جهاز متوافق على الأقل اثنين أو أكثر من سجلات البيانات وسجل تعليمات واحد.

تعليمات التسجيل

يستخدم سجل التعليمات للاحتفاظ بالتعليمات الحالية. لذلك يتم استخدام بياناته بواسطة وحدة التحكم في TAP لتحديد ما يجب تنفيذه بالإشارات التي يتم الحصول عليها. في أغلب الأحيان ، ستصف بيانات سجل التعليمات أي إشارات سجلات البيانات التي يجب تمريرها.

سجلات البيانات

تتوفر سجلات البيانات في ثلاثة أنواع: BSR (Boundary Scan Register) و BYPASS وسجل رموز المعرف ID. وأيضًا ، قد تكون هناك سجلات بيانات أخرى ، ولكنها ليست ضرورية كعنصر من عناصر معيار JTAG.

سجل مسح الحدود (BSR)

BSR هو سجل بيانات الاختبار الرئيسي الذي يتم استخدامه لتحويل البيانات من وإلى دبابيس الإدخال / الإخراج الخاصة بالجهاز.

BYPASS

التجاوز هو سجل أحادي البت يستخدم لتمرير البيانات من TDI - TDO. لذلك فهو يسمح باختبار الأجهزة الإضافية داخل الدائرة بأدنى حد من الحمل.

رموز الهوية

يتضمن هذا النوع من تسجيل البيانات رمز المعرف بالإضافة إلى رقم المراجعة للجهاز. لذلك تسمح هذه البيانات للجهاز بالاتصال بملف BSDL (لغة وصف مسح الحدود). تضمن هذا الملف تفاصيل تكوين Boundary Scan للجهاز.

عمل JTAG هو ، في البداية ، يتم اختيار وضع التعليمات حيث تتيح إحدى الحالات في هذا الوضع 'المسار' للمشغل الساعة ضمن تعليمات بواسطة TDI. بعد ذلك ، تتطور آلة الدولة حتى يتم إعادة ترتيبها. الخطوة التالية لمعظم التعليمات هي اختيار وضع البيانات. لذلك في هذا الوضع ، يتم تحميل البيانات من خلال TDI للقراءة من TDO. بالنسبة لـ TDI & TDO ، سيتم ترتيب مسارات البيانات وفقًا للتعليمات التي تم تسجيلها. بمجرد الانتهاء من عملية القراءة / الكتابة ، يتطور جهاز الحالة مرة أخرى إلى حالة إعادة التعيين.

الفرق بين JTAG مقابل UART

يشمل الفرق بين JTAG و UART ما يلي.

| JTAG |

UART |

| مصطلح 'JTAG' لتقف على مجموعة عمل الاختبار المشترك. | المصطلح ' UART 'لتقف على جهاز استقبال / مرسل عالمي غير متزامن. |

| إنها واجهة متزامنة تستخدم أجهزة مدمجة لبرمجة الفلاش . | UART هي واجهة غير متزامنة تستخدم أداة تحميل التشغيل التي تعمل داخل الذاكرة. |

| إنها مجموعة من منافذ الاختبار التي تستخدم لتصحيح الأخطاء ولكن يمكن استخدامها أيضًا لبرمجة البرامج الثابتة (وهو ما يتم عادةً).

|

UART هو نوع من الشرائح التي تتحكم في الاتصالات من وإلى الجهاز ، مثل متحكم دقيق ، ذاكرة القراءة فقط ، ذاكرة الوصول العشوائي ، وما إلى ذلك ، في معظم الأحيان ، هو اتصال تسلسلي يسمح لنا بالتواصل مع جهاز. |

| هذه متوفرة في أربعة أنواع TDI و TDO و TCK و TMS و TRST. | هذه متوفرة في نوعين غبي UART و FIFO UART. |

| Joint Test Action Group هي برمجة تسلسلية أو بروتوكول وصول إلى البيانات يتم استخدامه في واجهات وحدات التحكم الدقيقة والأجهزة ذات الصلة. | UART هو نوع واحد من الشرائح ، بخلاف ذلك ، المكون الفرعي للمتحكم الدقيق والذي يستخدم لتوفير الأجهزة لتوليد دفق تسلسلي غير متزامن مثل RS-232 / RS-485. |

| مكونات JTAG هي المعالجات ، FPGAs ، CPLDs ، إلخ. | مكونات UART هي مولد CLK ، وسجلات تحويل الإدخال / الإخراج ، ونقل أو استقبال المخازن المؤقتة ، ومخزن ناقل بيانات النظام ، وقراءة أو كتابة منطق التحكم ، إلخ. |

محلل بروتوكول JTAG

محلل بروتوكول JTAG مثل PGY-JTAG-EX-PD هو نوع واحد من محلل البروتوكول بما في ذلك بعض الميزات لالتقاط وتصحيح الاتصالات بين المضيف والتصميم قيد الاختبار. هذا النوع من المحلل هو الأداة الرائدة التي تسمح لمهندسي الاختبار والتصميم باختبار التصميمات الخاصة لـ JTAG لمواصفاتها من خلال ترتيب PGY-JTAG-EX-PD مثل Master أو Slave لإنشاء حركة مرور JTAG وفك تشفير حزم فك التشفير الخاصة بـ بروتوكول مجموعة عمل الاختبار المشترك.

سمات

تتضمن ميزات محلل بروتوكول JTAG ما يلي.

- يدعم ما يصل إلى 25 ميجا هرتز من ترددات JTAG.

- يولد حركة مرور JTAG وفك تشفير البروتوكول للحافلة في وقت واحد.

- لديها قدرة JTAG الرئيسية.

- سرعات بيانات JTAG المتغيرة ودورة العمل.

- تأخيرات TDI & TCK المعرفة من قبل المستخدم.

- الكمبيوتر المضيف USB 2.0 أو 3.0 واجهة.

- تحليل الخطأ داخل بروتوكول فك

- بروتوكول توقيت الحافلة التي تم فك ترميزها.

- دفق بيانات البروتوكول المستمر إلى الكمبيوتر المضيف لتوفير مخزن مؤقت كبير.

- قائمة أنشطة البروتوكول.

- بسرعات مختلفة ، يمكن كتابة نص تمرين للجمع بين توليد إطارات بيانات متعددة.

الرسم البياني توقيت

ال مخطط توقيت JTAG يتم عرض البروتوكول أدناه. في الرسم البياني التالي ، يظل دبوس TDO في حالة المعاوقة العالية باستثناء أثناء حالة تحكم shift-IR / shift-DR.

في ظروف تحكم shift-IR و Shift-DR ، يتم تحديث دبوس TDO على الحافة المتناقصة لـ TCK عبر الهدف وأخذ عينات على الحافة المتزايدة لـ TCK عبر المضيف.

يتم أخذ عينات من دبابيس TDI و TMS ببساطة على الحافة المتزايدة لـ TCK من خلال Target. تحديث على الحافة المتناقصة وإلا TCK من خلال المضيف.

التطبيقات

ال تطبيقات JTAG تشمل ما يلي.

- تستخدم مجموعة عمل الاختبار المشترك بشكل متكرر في المعالجات لتوفير حق الدخول إلى وظائف المحاكاة أو التصحيح.

- تستخدم جميع CPLDs & FPGAs هذا كواجهة لمنح الوصول إلى وظائف البرمجة الخاصة بهم.

- يتم استخدامه لاختبار ثنائي الفينيل متعدد الكلور دون الوصول المادي

- يتم استخدامه لاختبارات التصنيع على مستوى اللوحة.

وبالتالي ، هذا كل شيء عن لمحة عامة عن JTAG - تكوين دبوس ، العمل مع التطبيقات. يتم استخدام معيار الصناعة JTAG للتحقق من التصميم وكذلك اختبار ثنائي الفينيل متعدد الكلور بعد التصنيع. هنا سؤال لك ، JTAG تعني؟