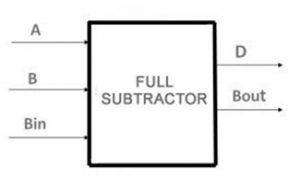

بشكل عام ، يعتبر الطرح الكامل واحدًا من أكثر الطرق استخدامًا و دوائر المنطق التوافقية الأساسية . إنه جهاز إلكتروني أساسي يستخدم لطرح رقمين ثنائيين. في المقالة السابقة ، قدمنا بالفعل النظرية الأساسية لـ أفعى نصف و أفعى كامل الذي يستخدم الأرقام الثنائية للحساب. وبالمثل ، يستخدم الطرح الكامل أرقامًا ثنائية مثل 0،1 للطرح. يمكن بناء دائرة هذا باستخدام بوابات منطقية مثل بوابة OR و Ex-OR و NAND. مدخلات هذا الطرح هي A و B و Bin والمخرجات هي D و Bout.

تقدم هذه المقالة فكرة نظرية مطروح كاملة تشتمل على المباني مثل ما هو الطرح ، والتصميم مع البوابات المنطقية ، وجدول الحقيقة ، وما إلى ذلك. هذه المقالة مفيدة لطلاب الهندسة الذين يمكنهم الاطلاع على هذه الموضوعات في مختبر HDL العملي.

ما هو الطرح؟

يمكن إجراء طرح الأرقام الثنائية بمساعدة دائرة الطرح. هذا نوع واحد من الدوائر المنطقية التوافقية ، تُستخدم لطرح رقمين ثنائيين مثل 0 و 1. لا يغير طرح الأرقام الثنائية من 0 إلى 0 أو من 0 إلى 1 النتيجة ، وسيؤدي طرح 1 إلى 1 إلى 0 ولكن طرح 1 إلى 0 يحتاج إلى الاقتراض.

على سبيل المثال ، تشتمل دائرة الطرح ثنائية البت على مدخلين مثل A & B في حين أن المخرجات هي الفرق والاقتراض. يمكن بناء هذه الدائرة باستخدام أدوات إضافة إلى جانب العاكسات الموجودة بين كل إدخال بيانات بالإضافة إلى مدخلات الاستعارة (Bin) للمرحلة السابقة من FA.

يتم تصنيف الطرح إلى نوعين مثل نصف مطروح وطرح كامل. نحن هنا نناقش المطرح الكامل.

ما هو الطرح الكامل؟

إنه جهاز إلكتروني أو دائرة المنطق الذي يقوم بطرح رقمين ثنائيين. إنها دائرة منطقية توافقية تستخدم في الإلكترونيات الرقمية. تتوفر العديد من الدوائر التوافقية في تكنولوجيا الدوائر المتكاملة وهي المضافات والمشفرات وأجهزة فك التشفير والمضاعفات. في هذه المقالة ، سنناقش بنائه باستخدام نصف مطروح وكذلك مصطلحات مثل جدول الحقيقة.

مطروح كامل

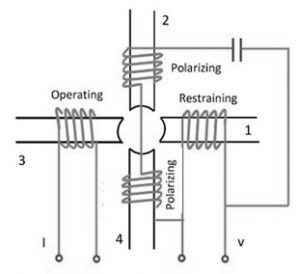

يمكن أن يتم تصميم هذا بواسطة اثنين من المطاحين النصفين ، والذي يتضمن ثلاثة مدخلات مثل minuend ، و subtrahend ، و استعارة ، ويتم الحصول على بت الاقتراض بين المدخلات من طرح رقمين ثنائيين ويتم طرحه من الزوج التالي ذي الترتيب الأعلى بت ، والمخرجات كفرق والاقتراض.

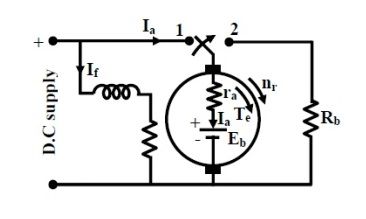

ال مخطط كتلة الطرح الكامل هو مبين أدناه. العيب الرئيسي للنصف المطروح هو أننا لا نستطيع عمل بت استعارة في هذا الطرح. بينما في تصميمه ، يمكننا في الواقع عمل جزء استعارة في الدائرة ويمكننا طرح ما تبقى من اثنين i / ps. هنا A هو الحد الأدنى ، B هو المطروح و Bin يتم الاقتراض فيه. النواتج هي الفرق (Diff) و Bout (استعارة). يمكن الحصول على دارة الطرح الكاملة باستخدام طائفي نصفين مع بوابة OR إضافية.

مخطط كامل لدائرة الطرح مع بوابات منطقية

ال رسم تخطيطي لدائرة الطرح الكامل باستخدام البوابة الأساسية يظهر s في مخطط الكتلة التالي. يمكن عمل هذه الدائرة بدائرتين نصف مطروح.

في دائرة نصف مطروح الأولية ، المدخلات الثنائية هي A و B. كما ناقشنا في مقالة half-Subtractor السابقة ، ستولد ناتجين هما الفرق (Diff) & Borrow.

الطرح الكامل باستخدام البوابات المنطقية

يتم إعطاء الفرق o / p للمطرح الأيسر إلى دائرة نصف الدائرة اليسرى. يتم توفير ناتج Diff أيضًا لمدخلات النصف الأيمن من دائرة Subtractor. قدمنا الاقتراض قليلاً عبر i / p الآخر في التالي نصف دائرة الطرح . مرة أخرى ، ستعطي فرقًا بالإضافة إلى استعارة الجزء. الناتج النهائي لهذا الطرح هو Diff-output.

من ناحية أخرى ، فإن Borrow من كل من دائرتي Subtractor النصفية متصلان بالبوابة المنطقية OR. في وقت لاحق من إعطاء منطق أو لقطتين من وحدات الإخراج للطرح ، نحصل على الاقتراض النهائي من المطروح. آخر استعارة للدلالة على MSB (أهم بت).

إذا لاحظنا الدائرة الداخلية لهذا ، فيمكننا رؤية جزأين نصفين مع بوابة NAND وبوابة XOR مع بوابة OR إضافية.

جدول حقيقة المطروح الكامل

هذه دائرة الطرح ينفذ عملية طرح بين بتتين ، والتي تحتوي على 3 مدخلات (A و B و Bin) ومخرجات (D و Bout). هنا تشير المدخلات إلى الحد الأدنى ، والعرض الفرعي ، والاقتراض السابق ، في حين يتم الإشارة إلى المخرجين على أنهما استعارة / ع والفرق. تُظهر الصورة التالية جدول الحقيقة للطرح الكامل.

المدخلات | النواتج | |||

مينويند (أ) | المطروح (م) | استعارة (سلة) | الفرق (د) | استعارة (نوبة) |

0 | 0 | 0 | 0 | 0 |

0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

1 | 1 | 0 | 0 | 0 |

1 | 1 | 1 | 1 | 1 |

K- خريطة

تبسيط ملف الطرح الكامل K- الخريطة للفرق والاقتراض أعلاه موضح أدناه.

معادلات الفرق وكذلك Bin مذكورة أدناه.

التعبير عن الاختلاف هو ،

D = A’B’Bin + AB’Bin ’+ A’BBin’ + ABBin

التعبير عن الاستعارة هو ،

بوت = A’Bin + A’B + BBin

المتتالية لدائرة الطرح الكاملة

في السابق ، ناقشنا نظرة عامة على هذا مثل البناء ، مخطط الدائرة مع البوابات المنطقية. ولكن إذا أردنا طرح رقمين آخرين من 1 بت ، فإن دائرة الطرح هذه مفيدة جدًا في تسلسل أرقام بت واحد وطرح أكثر من رقمين ثنائيين. في مثل هذه الحالات ، يتم استخدام دائرة متتالية كاملة الأفعى بمساعدة البوابة المنطقية NOT. يمكن أن يتم تحويل الدائرة من جامع كامل إلى مطروح كامل باستخدام تقنية 2 التكميلية.

بشكل عام ، قم بعكس مدخلات المطروح للأداة الكاملة باستخدام بوابة NOT وبخلاف ذلك العاكس. من خلال إضافة هذا Minuend (إدخال غير مقلوب) و Subtrahend (إدخال مقلوب) ، فإن LSB (إدخال الإدخال) لدائرة FA هو 1 ، مما يعني ارتفاع المنطق وإلا فإننا نطرح رقمين ثنائيين باستخدام تقنية 2 المكمل. ناتج FA هو بت Diff وإذا عكسنا التنفيذ فيمكننا الحصول على MSB وإلا استعارة بت. في الواقع ، يمكننا تصميم الدائرة بحيث يمكن ملاحظة هذا الإخراج.

كود فيريلوج

بالنسبة لجزء الترميز ، نحتاج أولاً إلى التحقق من الطريقة الهيكلية لنمذجة مخطط الدائرة المنطقية. يمكن بناء الرسم التخطيطي المنطقي لهذا باستخدام بوابة AND ، نصف دوائر الطرح ، ومجموعة من البوابات المنطقية مثل بوابات AND ، OR ، NOT ، XOR. كما هو الحال في النمذجة الهيكلية ، نشرح وحدات مختلفة لكل ترتيب عنصري أساسي. في الكود التالي ، يمكن تحديد وحدات مختلفة لكل بوابة.

هذه الوحدة هي لبوابة OR.

المدخلات: a0، b0

الإخراج: c0

أخيرًا ، سنقوم بتوحيد هذه الوحدات الدقيقة للبوابة في وحدة نمطية واحدة فقط. لذلك ، هنا نستخدم إنشاء مثيل للوحدة. الآن يمكن استخدام هذا إنشاء مثيل بمجرد أن نرغب في تكرار وحدة أو وظيفة محددة لمجموعات إدخال متنوعة. أولاً ، نصمم نصف مطروح ، ثم تستخدم هذه الوحدة لتنفيذ مطروح كاملة. لتنفيذ ذلك ، نستخدم بوابة OR للجمع بين o / ps لمتغير Bout. ال كود فيريلوج للطرح الكامل هو مبين أدناه

وحدة or_gate (a0 ، b0 ، c0)

الإدخال a0 ، b0

الإخراج c0

تعيين c0 = a0 | ب 0

الوحدة النهائية

الوحدة النمطية xor_gate (a1 ، b1 ، c1)

الإدخال a1 ، b1

الإخراج c1

تعيين c1 = a1 ^ b1

الوحدة النهائية

الوحدة النمطية and_gate (a2 ، b2 ، c2)

الإدخال a2 ، b2

الإخراج c2

تعيين c2 = a2 & b2

الوحدة النهائية

الوحدة النمطية not_gate (a3 ، b3)

المدخلات a3

الإخراج b3

تعيين b3 = ~ a3

الوحدة النهائية

وحدة half_subtractor (a4 ، b4 ، c4 ، d4)

الإدخال a4 ، b4

الإخراج c4 ، d4

سلك x

xor_gate u1 (a4، b4، c4)

and_gate u2 (x، b4، d4)

not_gate u3 (a4، x)

الوحدة النهائية

الوحدة النمطية full_subtractor (A ، B ، Bin ، D ، Bout)

المدخلات أ ، ب ، بن

الإخراج د ، بوت

سلك ف ، ف ، ص

half_subtractor u4 (A، B، p، q)

half_subtractor u5 (p، Bin، D، r)

or_gate u6 (q، r، Bout)

الوحدة النهائية

مطروح كاملة باستخدام معدد 4X1

يمكن تنفيذ عملية الطرح من خلال الطريقة التكميلية للاثنين. وبالتالي فإننا نحتاج إلى استخدام بوابة 1-XOR والتي تستخدم لعكس 1 بت وتضمين واحدة في بتة حمل. يشبه ناتج DIFFERENCE الناتج SUM في دائرة الأفعى الكاملة ، لكن BARROW o / p لا يشبه إخراج حمل الأفعى الكامل ، ومع ذلك فهو مقلوب ومكمل ، مثل A - B = A + (-B) = مكمل أ + اثنان من ب.

يظهر تصميم هذا باستخدام معدد إرسال 4X1 في الرسم البياني المنطقي التالي. يمكن إجراء هذا التصميم باستخدام الخطوات التالية.

4X1 معدد

- في الخطوة 1 ، يوجد ناتجان مثل Sub و Borrow. لذلك علينا أن نختار 2 معدد إرسال.

- في الخطوة 2 ، يمكن تنفيذ جدول الحقيقة جنبًا إلى جنب مع خرائط K

- في الخطوة 3 ، يمكن تحديد المتغيرين كخط التحديد الخاص بك. على سبيل المثال ، B & C في هذه الحالة.

جدول الحقيقة

ال جدول الحقيقة للطرح الكامل تتضمن الدائرة باستخدام معدد إرسال 4X1 ما يلي

إلى | ب | ج | الفرعية | تقترض |

0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

1 | 1 | 1 | 1 | 1 |

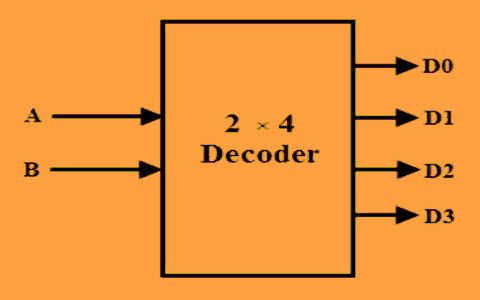

الطرح الكامل باستخدام وحدة فك الترميز

يمكن تصميم جهاز طرح كامل باستخدام 3-8 مفكك تشفير باستخدام مخرجات منخفضة نشطة. لنفترض أن وحدة فك التشفير تعمل باستخدام المخطط المنطقي التالي. يشتمل مفكك الشفرة على ثلاثة مدخلات في 3-8 مفكك تشفير. بناءً على جدول الحقيقة ، يمكننا كتابة المصطلحات لمخرجات الاختلاف والاقتراض.

من جدول الحقيقة أعلاه ،

بالنسبة للوظائف المختلفة في جدول الحقيقة ، يمكن كتابة minterms كـ 1،2،4،7 ، وبالمثل ، بالنسبة للاقتراض ، يمكن كتابة minterms كـ 1،2،3،7. تشتمل وحدات فك التشفير من 3 إلى 8 على ثلاثة مدخلات بالإضافة إلى 8 مخرجات مثل 0 إلى 7 أرقام.

3-to-8 Decoder

إذا كان إدخال الطرح هو 000 ، فسيكون الناتج '0' نشطًا وإذا كان الإدخال 001 ، فسيكون الناتج '1' نشطًا.

الآن يمكن أخذ نواتج الطرح من 1 و 2 و 4 و 7 لتوصيله ببوابة NAND ، ثم سيكون الناتج هو الفرق. يمكن توصيل هذه المخرجات ببوابات NAND المنطقية الأخرى حيث يتغير الناتج إلى الاقتراض.

على سبيل المثال ، إذا كان الإدخال 001 ، فسيكون الناتج 1 وهذا يعني أنه نشط. لذا فإن الناتج نشط منخفض ويمكن الحصول على الإخراج من بوابة NAND التي تسمى وظيفة الاختلاف مثل وظيفة عالية والاقتراض تتغير أيضًا لتكون عالية. لذلك نحصل على الإخراج المفضل. أخيرًا ، يعمل مفكك الشفرة كطرح كامل.

المميزات والعيوب

ال مزايا الطرح تشمل ما يلي.

- تصميم الطرح بسيط للغاية وكذلك تنفيذه

- خصم الطاقة داخل DSP (معالجة الإشارات الرقمية)

- يمكن تنفيذ المهام الحسابية بسرعة عالية.

ال مساوئ الطرح تشمل ما يلي.

- في المطروح النصفية ، لا يوجد شرط لقبول مدخلات تشبه الاقتراض من المرحلة السابقة.

- يمكن أن تكون سرعة الطرح جزئية من خلال التأخير في الدائرة.

التطبيقات

قليلا من ال تطبيقات الطرح الكامل تشمل ما يلي

- تستخدم هذه بشكل عام في ALU (وحدة المنطق الحسابي) في أجهزة الكمبيوتر للطرح كوحدة المعالجة المركزية ووحدة معالجة الرسومات لتطبيقات الرسومات لتقليل صعوبة الدائرة.

- تُستخدم الطوابع في الغالب لأداء وظائف حسابية مثل الطرح ، في الآلات الحاسبة الإلكترونية وكذلك الأجهزة الرقمية.

- هذه قابلة للتطبيق أيضًا ميكروكنترولر مختلفة للطرح الحسابي ، وأجهزة ضبط الوقت ، وعداد البرنامج (PC)

- تستخدم الطوابع في المعالجات لحساب الجداول والعناوين وما إلى ذلك.

- وهو مفيد أيضًا لأنظمة DSP والأنظمة القائمة على الشبكات.

- تُستخدم هذه بشكل أساسي في ALU داخل أجهزة الكمبيوتر لطرح مثل CPU و GPU لتطبيقات الرسومات لتقليل تعقيد الدائرة.

- تستخدم هذه بشكل أساسي لأداء الوظائف الحسابية مثل الطرح داخل الأجهزة الرقمية والآلات الحاسبة وما إلى ذلك.

- هذه الطرح مناسبة أيضًا للعديد من المتحكمات الدقيقة لأجهزة ضبط الوقت وأجهزة الكمبيوتر (عداد البرامج) والطرح الحسابي

- يتم استخدام هذه المعالجات لحساب العناوين والجداول وما إلى ذلك.

- يمكن تنفيذ هذا باستخدام بوابات منطقية مثل NAND & NOR مع أي دائرة منطقية كاملة للطرح لأن كل من بوابات NOR و NAND تسمى بوابات عالمية.

من المعلومات المذكورة أعلاه ، من خلال تقييم الأفعى ، المطروح الكامل باستخدام دائرتين نصفيتين ، وأشكاله المجدولة ، يمكن للمرء أن يلاحظ أن Dout في المطروح الكامل يشبه بدقة Sout of the full-adder. الاختلاف الوحيد هو أن A (متغير الإدخال) يكمل في المطروح الكامل. وبالتالي ، من الممكن تغيير دائرة الأفعى الكاملة إلى مطروح كامل فقط من خلال استكمال i / p A قبل إعطائها البوابات المنطقية لتوليد آخر إخراج بت استعارة (بوت).

باستخدام أي دائرة منطقية كاملة للطرح ، يمكن تنفيذ مطروح كامل باستخدام بوابات NAND وطرح كامل باستخدام أو بوابات ، حيث يتم التعامل مع كل من بوابات NAND و NOR كبوابات عالمية. إليك سؤال لك ، ما الفرق بين أنصاف مطروح وطرح كامل؟