في مجال الإلكترونيات ، فإن المفهوم الأكثر أهمية الذي يعمل عليه كل مكون هو ' بوابات المنطق، بوابات منطقية '. حيث يتم تنفيذ مفهوم البوابات المنطقية في كل وظيفة مثل الدوائر المتكاملة ، وأجهزة الاستشعار ، وأغراض التبديل ، والميكروكونترولر والمعالجات ، وأغراض التشفير وفك التشفير ، وغيرها. بالإضافة إلى ذلك ، هناك تطبيقات واسعة لبوابات المنطق. هناك العديد من أنواع البوابات المنطقية مثل Adder و Subtractor و Full الأفعى ، مطروح كامل ، نصف مطروح ، وغيرها الكثير. لذلك ، توفر هذه المقالة معلومات جماعية عن نصف دائرة الطرح و نصف جدول الحقيقة المطروح والمفاهيم ذات الصلة.

ما هو Half Subtractor؟

قبل الخوض في مناقشة نصف المطروح ، علينا معرفة الطرح الثنائي. في عملية الطرح الثنائي ، تشبه عملية الطرح عملية الطرح الحسابي. في الطرح الحسابي ، يتم استخدام نظام رقم الأساس 2 بينما في الطرح الثنائي ، يتم استخدام الأرقام الثنائية للطرح. يمكن الإشارة إلى المصطلحات الناتجة بالاختلاف والاقتراض.

نصف الطرح هو الأكثر أهمية دائرة المنطق التوافقي الذي يستخدم في الالكترونيات الرقمية . في الأساس ، هذا جهاز إلكتروني أو بعبارات أخرى ، يمكننا القول إنه دائرة منطقية. تُستخدم هذه الدائرة لإجراء طرح رقمين ثنائيين. في المقال السابق ، ناقشنا بالفعل مفاهيم نصف الأفعى ودائرة الأفعى الكاملة الذي يستخدم الأرقام الثنائية للحساب. وبالمثل ، تستخدم دائرة الطرح أرقامًا ثنائية (0،1) للطرح. يمكن بناء دائرة نصف الطرح مع اثنين بوابات منطقية وهي بوابات NAND و EX-OR . تعطي هذه الدائرة عنصرين مثل الفرق وكذلك الاقتراض.

كما هو الحال في الطرح الثنائي ، فإن الرقم الرئيسي هو 1 ، يمكننا استعارة بينما يتفوق Subrahend 1 على الحد الأدنى 0 ونتيجة لذلك ، ستحتاج إلى الاقتراض. يعطي المثال التالي الطرح الثنائي لبتين ثنائيين.

الرقم الأول | الرقم الثاني | اختلاف | تقترض |

0 | 0 | 0 | 0 |

1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 |

في عملية الطرح أعلاه ، يمكن تمثيل الرقمين بـ A و B. يمكن طرح هذين الرقمين وإعطاء البتات الناتجة كفرق واستعارة.

عندما نلاحظ الصفين الأولين والرابع ، يكون الفرق بين هذين الصفين ، فإن الفرق والاقتراض متشابهان لأن المطروح أقل من الحد الأدنى. وبالمثل ، عندما نلاحظ الصف الثالث ، يتم طرح القيمة الصغرى من المطروح. لذا فإن بتات الفرق والاقتراض هي 1 لأن رقم المطروح أعلى من الرقم الأصغر.

هذه الدائرة التوافقية هي أداة أساسية لأي نوع من دارة رقمية لمعرفة التوليفات الممكنة للمدخلات والمخرجات. على سبيل المثال ، إذا كان للطرح مدخلين ، فستكون المخرجات الناتجة أربعة. تم ذكر o / p للطرح النصف في الجدول أدناه والذي سيشير إلى بت الفرق وكذلك بت الاقتراض. يمكن إجراء تفسير جدول الحقيقة للدائرة باستخدام البوابات المنطقية مثل البوابة المنطقية EX-OR وتشغيل البوابة AND متبوعة بالبوابة NOT.

حل جدول الحقيقة باستخدام K- خريطة هو مبين أدناه.

نصف مطروح ك خريطة

ال نصف تعبير مطروح يمكن اشتقاق استخدام جدول الحقيقة وخريطة K كـ

اختلاف (د) = ( x’y + س ص ')

= س ⊕ ص

استعارة (B) = x’y

الدائرة المنطقية

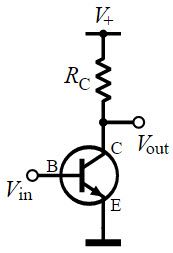

ال نصف الدائرة المنطقية الطرح يمكن تفسيره باستخدام البوابات المنطقية:

- 1 بوابة XOR

- 1 ليس بوابة

- 1 و البوابة

التمثيل

نصف الدائرة المنطقية للطارئ

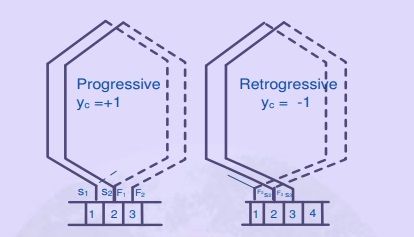

مخطط كتلة نصف الطرح

يظهر مخطط كتلة نصف الطرح أعلاه. يتطلب مدخلين وكذلك يعطي مخرجات. هنا يتم تمثيل المدخلات بـ A & B ، والمخرجات هي الفرق والاقتراض.

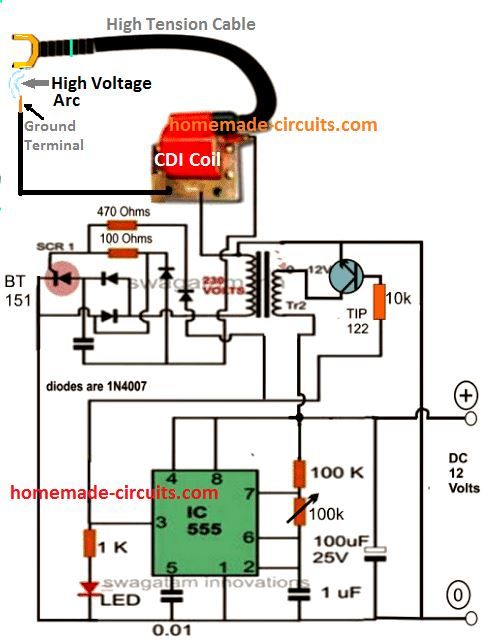

يمكن تصميم الدائرة أعلاه ببوابات EX-OR & NAND. هنا ، يمكن بناء بوابة NAND باستخدام بوابات AND وليس. لذلك نحن بحاجة إلى ثلاث بوابات منطقية لعمل نصف دائرة مطروح وهي بوابة EX-OR ، بوابة NOT ، وبوابة NAND.

مزيج من بوابة AND و NOT ينتج بوابة مشتركة مختلفة تسمى NAND Gate. سيكون خرج Ex-OR gate هو بت الفرق وسيكون ناتج NAND Gate هو بت Borrow bit لنفس المدخلات A & B.

والبوابة

AND-gate هي نوع واحد من البوابات المنطقية الرقمية ذات مدخلات متعددة ومخرج واحد ، وبناءً على مجموعات المدخلات ، ستقوم بتنفيذ الاقتران المنطقي. عندما تكون جميع مدخلات هذه البوابة عالية ، سيكون الناتج مرتفعًا وإلا سيكون الناتج منخفضًا. يظهر الرسم التخطيطي المنطقي لبوابة AND مع جدول الحقيقة أدناه.

وجدول البوابة والحقيقة

ليس بوابة

البوابة NOT هي نوع واحد من البوابات المنطقية الرقمية ذات مدخل واحد وبناءً على المدخلات سيتم عكس الإخراج. على سبيل المثال ، عندما يكون دخل البوابة NOT مرتفعًا ، يكون الناتج منخفضًا. يظهر الرسم التخطيطي المنطقي لـ NOT-gate مع جدول الحقيقة أدناه. باستخدام هذا النوع من البوابة المنطقية ، يمكننا تنفيذ بوابات NAND و NOR.

لا بوابة وجدول الحقيقة

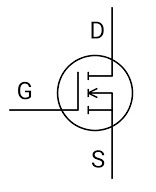

بوابة OR السابقة

بوابة Exclusive-OR أو EX-OR هي نوع واحد من البوابة المنطقية الرقمية ذات دخلين ومخرج واحد. يعتمد عمل هذه البوابة المنطقية على بوابة OR. إذا كان أي من مدخلات هذه البوابة مرتفعًا ، فسيكون خرج البوابة EX-OR مرتفعًا. يتم عرض رمز وجدول الحقيقة لـ EX-OR أدناه.

بوابة XOR وجدول الحقيقة

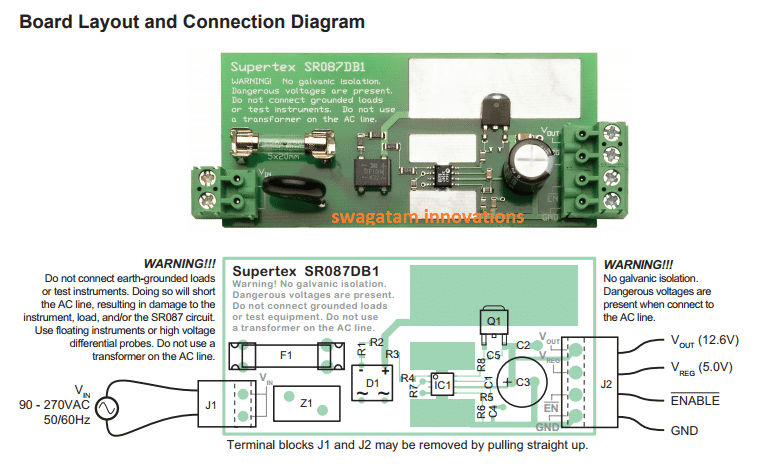

نصف دائرة الطرح باستخدام بوابة Nand

يمكن أن يتم تصميم الطرح بواسطة باستخدام البوابات المنطقية مثل بوابة NAND وبوابة Ex-OR. من أجل تصميم نصف دائرة الطرح هذه ، يجب أن نعرف المفهومين وهما الاختلاف والاستعارة.

نصف دائرة الطرح باستخدام بوابة Nand

إذا قمنا بالمراقبة بحذر ، فمن الواضح إلى حد ما أن تنوع العمليات التي تنفذها هذه الدائرة والتي ترتبط بدقة بعملية بوابة EX-OR. لذلك ، يمكننا ببساطة استخدام بوابة EX-OR لإحداث فرق. بالطريقة نفسها ، يمكن تحقيق الاقتراض الناتج عن نصف دائرة الأفعى ببساطة عن طريق استخدام مزيج من البوابات المنطقية مثل AND- gate و NOT-gate.

يمكن أيضًا تصميم هذا النظام المنسق باستخدام بوابات NOR حيث يتطلب 5 بوابات NOR للبناء. يظهر مخطط نصف مخطط الدائرة باستخدام بوابات NOR على النحو التالي:

نصف مطروح باستخدام ولا بوابات

جدول الحقيقة

أول بت | البتة الثانية | اختلاف (خارج أو خارج) | تقترض (ناند خارج) |

0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 |

VHDL ورمز Testbench

يتم شرح كود VHDL لنصف الطرح على النحو التالي:

مكتبة IEEE

استخدم IEEE.STD_LOGIC_1164.ALL

استخدم IEEE.STD_LOGIC_ARITH.ALL

استخدم IEEE.STD_LOGIC_UNSIGNED.ALL

الكيان Half_Sub1 هو

المنفذ (أ: في STD_LOGIC

ب: في STD_LOGIC

HS_Diff: خارج STD_LOGIC

HS_Borrow: out STD_LOGIC)

نهاية Half_Sub1

السلوك المعماري لـ Half_Sub1 هو

يبدأ

HS_Diff<=a xor b

HS_Borrow<=(not a) and b

ال رمز testbench لـ HS موضح على النحو التالي:

مكتبة IEEE

استخدم ieee.std_logic_1164.ALL

ENTITY HS_tb IS

نهاية HS_tb

هندسة HS_tb من HS_tb IS

مكون HS

المنفذ (a: IN std_logic

ب: IN std_logic

HS_Diff: OUT std_logic

HS_Borrow: OUT std_logic

)

المكون النهائي

إشارة أ: std_logic: = '0'

إشارة ب: std_logic: = '0'

إشارة HS_Diff: std_logic

إشارة HS_Borrow: std_logic

يبدأ

جديد: HS PORT MAP (

أ => أ ،

ب => ب ،

HS_Diff => HS_Diff ،

HS_borrow => HS_borrow

)

stim_proc: عملية

يبدأ

إلى<= ‘0’

ب<= ‘0’

انتظر 30 نانوثانية

إلى<= ‘0’

ب<= ‘1’

انتظر 30 نانوثانية

إلى<= ‘1’

ب<= ‘0’

انتظر 30 نانوثانية

إلى<= ‘1’

ب<= ‘1’

انتظر

إنهاء العملية

نهاية

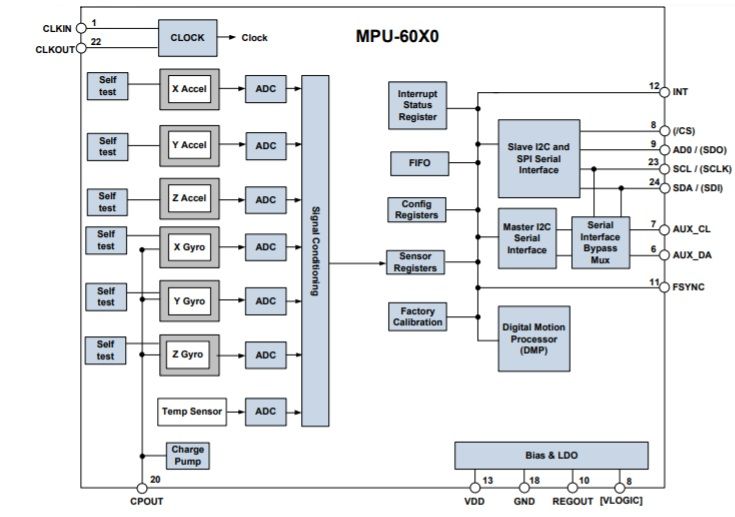

الطرح الكامل باستخدام نصف الطرح

المطروح الكامل هو جهاز تجميعي يقوم بتشغيل وظيفة الطرح باستخدام بتتين وهو مطروح وطرح. تعتبر الدائرة استعارة المخرجات السابقة ولها ثلاثة مدخلات بمخرجين. المدخلات الثلاثة هي الحد الأدنى ، المطروح والمدخلات المستلمة من المخرجات السابقة التي تم استعارتها والمخرجات هما الفرق والاقتراض.

الرسم التخطيطي المنطقي الكامل للمطور

جدول الحقيقة ل مطروح كامل يكون

| المدخلات | النواتج | |||

| X | ص | يين | FS_ الفرق | FS_Borrow |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

مع جدول الحقيقة أعلاه ، الرسم التخطيطي المنطقي للدوائر الإعلانية لتنفيذ الطرح الكامل باستخدام نصف الطرح موضح أدناه:

الطرح الكامل باستخدام النظام المنسق

مزايا وقيود نصف المطروح

مزايا نصف الطرح هي:

- تنفيذ وبناء هذه الدائرة بسيط وسهل

- تستهلك هذه الدائرة الحد الأدنى من الطاقة في معالجة الإشارات الرقمية

- يمكن إجراء الوظائف الحسابية بمعدلات سرعة محسنة

حدود هذه الدائرة التوافقية هي:

على الرغم من وجود تطبيقات مكثفة لنصف الطرح في العديد من العمليات والوظائف ، إلا أن هناك قيودًا قليلة وهي:

- لن تقبل دوائر الطرح النصفية 'الاقتراض' من المخرجات السابقة حيث يكون هذا هو العيب الأساسي لهذه الدائرة

- نظرًا لأن العديد من تطبيقات الوقت الفعلي تعمل على طرح عدد كبير من البتات ، فإن أجهزة الطرح النصفية لا تمتلك أي قدرة على طرح العديد من البتات

تطبيقات نصف مطروح

تطبيقات نصف الطرح تشمل ما يلي.

- يستخدم نصف الطرح لتقليل قوة إشارات الصوت أو الراديو

- يمكن أن يكون تستخدم في مكبرات الصوت لتقليل تشويه الصوت

- نصف المطروح هو يستخدم في وحدة المعالجة المركزية للمعالج

- يمكن استخدامه لزيادة وتقليل المشغلين وأيضًا لحساب العناوين

- يتم استخدام مطروح نصف لطرح أرقام الأعمدة الأقل أهمية. لطرح الأرقام متعددة الأرقام ، يمكن استخدامها في LSB.

لذلك ، من نظرية نصف الطرح أعلاه ، أخيرًا ، يمكننا إغلاق ذلك باستخدام هذه الدائرة يمكننا أن نطرح من بت ثنائي من أخرى لتوفير مخرجات مثل الفرق والاقتراض. وبالمثل ، يمكننا تصميم نصف مطروح باستخدام دارة بوابات NAND وكذلك بوابات NOR. المفاهيم الأخرى التي يجب معرفتها هي ما هو نصف رمز فيريلوج الطرح وكيف يمكن رسم الرسم التخطيطي RTL؟