هناك أنواع مختلفة من العائلات المنطقية المتاحة والتي تستخدم في تصميم الدوائر المنطقية الرقمية؛ منطق الترانزستور المقاوم (RTL)، ومنطق الباعث المقترن (ECL)، ومنطق ترانزستور الصمام الثنائي (DTL)، ومنطق أشباه الموصلات لأكسيد المعدن التكميلي (CMOS)، و منطق الترانزستور-الترانزستور (TTL) . ومن بين هذه العائلات المنطقية، تم استخدام عائلة المنطق DTL بشكل شائع قبل ستينيات وسبعينيات القرن العشرين لتحل محل العائلات المنطقية الأكثر تقدمًا مثل كموس و تي تي ال. منطق الترانزستور الثنائي هو فئة من الدوائر الرقمية الذي تم تصميمه مع الثنائيات والترانزستورات. لذا فإن الجمع بين الثنائيات والترانزستورات يسمح بعمل وظائف منطقية معقدة بمكونات صغيرة جدًا. توفر هذه المقالة معلومات موجزة عن DTL أو منطق الترانزستور الصمام الثنائي وتطبيقاتها.

ما هو منطق الترانزستور ديود؟

منطق ترانزستور الصمام الثنائي هو دائرة منطقية تنتمي إلى عائلة المنطق الرقمي والتي تستخدم لإنشاء دوائر رقمية. يمكن تصميم هذه الدائرة باستخدام الثنائيات والترانزستورات حيث يتم استخدام الثنائيات في جانب الإدخال وتستخدم الترانزستورات في جانب الإخراج، وبالتالي يعرف باسم DTL. DTL هي فئة محددة من الدوائر المستخدمة في الإلكترونيات الرقمية الحالية لمعالجة الإشارات الكهربائية.

في هذه الدائرة المنطقية، تكون الثنائيات مفيدة في أداء الوظائف المنطقية، بينما تستخدم الترانزستورات لأداء وظائف التضخيم. يتمتع DTL بالعديد من الفوائد مقارنة بـ المقاوم منطق الترانزستور مثل؛ وبالتالي، فإن قيم التهوية الأعلى وهامش الضوضاء العالي، يتم استبدال DTL بعائلة RTL. ال خصائص منطق الصمام الثنائي الترانزستور تشمل بشكل رئيسي؛ عديم الثقافة الرقمية، واستراتيجي رقمي، ومهندس رقمي، وأسرع تنظيميًا، ومركزًا للعملاء، ومدافعًا عن البيانات، ومنسقًا رقميًا لأماكن العمل، ومُحسِّنًا للعمليات التجارية.

الدائرة المنطقية للترانزستور الثنائي

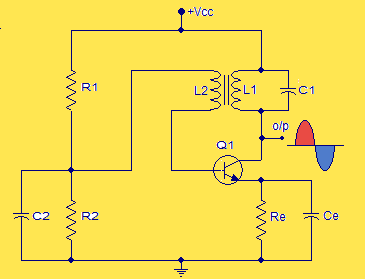

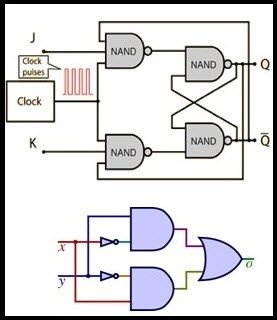

تظهر الدائرة المنطقية للترانزستور الثنائي أدناه. هذه عبارة عن دائرة بوابة NAND ذات ترانزستور ثنائي الصمام الثنائي. تم تصميم هذه الدائرة بثنائيين وترانزستور حيث يشار إلى الثنائيات بـ D1 و D2 ويشار إلى المقاوم بـ R1 الذي يشكل جانب الإدخال للدائرة المنطقية. يشكل تكوين الترانزستور Q1 CE والمقاوم R2 جانب الإخراج. يتم استخدام المكثف 'C1' في هذه الدائرة لإعطاء تيار زائد طوال فترة التبديل وهذا يقلل من وقت التبديل إلى مستوى معين.

العمل المنطقي للترانزستور الثنائي

عندما تكون مدخلات الدائرتين A وB منخفضة، فإن كلا الثنائيات D1 وD2 سوف يصبحان متحيزين للأمام، وبالتالي فإن هذه الثنائيات سوف تعمل في الاتجاه الأمامي. وبالتالي فإن مصدر التيار بسبب مصدر الجهد (+VCC = 5V) سوف يزود GND عبر المقاوم R1 والثنائيين. يتم تقليل مصدر الجهد داخل المقاومة R1 ولن يكون كافيًا تشغيل الترانزستور Q1، وبالتالي سيكون الترانزستور Q1 في وضع القطع. لذا، فإن o/p عند الطرف 'Y' سيكون منطقيًا 1 أو قيمة عالية.

عندما يكون أي من المدخلات منخفضًا، فإن الصمام الثنائي المقابل سيكون متحيزًا للأمام، لذا ستحدث عملية مماثلة. نظرًا لأن أيًا من هذه الثنائيات متحيز للأمام، فسيتم توفير التيار إلى الأرض عبر الصمام الثنائي المتحيز للأمام، وبالتالي سيكون الترانزستور 'Q1' في وضع القطع، وبالتالي فإن الخرج عند الطرف 'Y' سيكون عالية أو المنطق 1.

عندما يكون كلا المدخلين A وB مرتفعين، فإن كلا الثنائيات سوف تكون متحيزة عكسيًا، وبالتالي لن يتم توصيل كلا الثنائيات. لذلك في هذه الحالة، سيكون الجهد الكهربي من مصدر +VCC كافيًا لدفع الترانزستور Q1 إلى وضع التوصيل.

لذلك يوصل الترانزستور عبر أطراف الباعث والمجمع. يتم تقليل الجهد بالكامل داخل المقاوم 'R2' وسيكون الخرج عند الطرف 'Y' منخفضًا o/p ويعتبر منخفضًا أو منطقيًا 0.

جدول الحقيقة

يظهر جدول الحقيقة DTL أدناه.

|

أ |

ب | و |

|

0 |

0 | 1 |

|

0 |

1 |

1 |

| 1 | 0 |

1 |

| 1 | 1 |

0 |

تأخير الانتشار المنطقي للترانزستور الثنائي كبير جدًا. عندما تكون جميع المدخلات عالية منطقية، فإن الترانزستور سوف يدخل في حالة التشبع ويتراكم الشحن داخل المنطقة الأساسية. عندما يكون أحد المدخلات منخفضًا، يجب إزالة هذه الشحنة، مما يؤدي إلى تغيير وقت الانتشار. لتسريع منطق ترانزستور الصمام الثنائي بطريقة واحدة، يتم ذلك عن طريق إضافة مكثف عبر المقاوم R3. هنا، يساعد هذا المكثف في إيقاف تشغيل الترانزستور عن طريق التخلص من الشحنة المتراكمة في الطرف الأساسي. يساعد المكثف الموجود في هذه الدائرة أيضًا في تشغيل الترانزستور من خلال تعزيز المحرك الأساسي الأول.

تعديل منطق الترانزستور ديود

تظهر أدناه بوابة DTL NAND المعدلة. من الصعب جدًا تصنيع القيم الكبيرة لمكونات المقاومات والمكثفات اقتصاديًا على الدائرة المتكاملة. لذلك يمكن تعديل دائرة بوابة DTL NAND التالية لتنفيذ IC عن طريق إزالة المكثف C1 ببساطة، وتقليل قيم المقاوم واستخدام الترانزستورات والثنائيات حيثما أمكن ذلك. تستخدم هذه الدائرة المعدلة ببساطة مصدرًا موجبًا واحدًا وتتضمن هذه الدائرة مرحلة إدخال مع الثنائيات D1 وD2 ومقاوم R3 وبوابة AND التي يتم اتباعها من خلال عاكس ترانزستور.

عمل

عمل هذه الدائرة هو أن هذه الدائرة تحتوي على طرفي إدخال A وB، ويمكن أن تكون جهود الإدخال مثل A & B إما عالية أو منخفضة.

إذا كان كلا المدخلين A وB منخفضين أو منطقيين 0، فإن كلا الثنائيين سوف يتجهان نحو الأمام، وبالتالي فإن الجهد عند 'M' هو انخفاض جهد أحد الصمامات الثنائية الذي يبلغ 0.7 فولت. على الرغم من دفع الترانزستور 'Q' إلى التوصيل ، ثم نحتاج إلى 2.1 فولت لتوجيه الثنائيات D3 و D4 والوصلة BE للترانزستور 'Q'، وبالتالي فإن هذا الترانزستور هو القطع ويوفر الإخراج Y = 1

Y = Vcc = المنطق 1 وبالنسبة لـ A = B = 0، فإن Y = 1 أو High.

إذا كان أي من المدخلات A أو B منخفضًا، فيمكن توصيل أي من المدخلات بـ GND مع أي طرف متصل بـ +Vcc، وسيقوم الصمام الثنائي المكافئ بالتوصيل، وسيتم قطع الترانزستور VM ≅ 0.7 V & Q ، وقم بتوفير الإخراج 'Y' = 1 أو المنطق عالي.

إذا كان A = 0 & B = 1 (أو) إذا كان A = 1 & B = 0، فاخرج Y = 1 أو HIGH.

إذا كان هناك مدخلين مثل A & B مرتفعان وكان كل من A & B متصلين ببساطة بـ + Vcc، فإن كلا الثنائيات D1 و D2 ستكون ذات قاعدة عكسية ولا تقوم بالتوصيل. الثنائيات D3 وD4 متحيزة للأمام ويتم توفير التيار عند الطرف الأساسي ببساطة إلى ترانزستور Q من خلال Rd وD3 وD4. يمكن دفع الترانزستور إلى حالة التشبع وسيكون جهد o/p جهدًا منخفضًا.

بالنسبة لـ A = B = 1، يكون الإخراج Y = 0 أو LOW.

تتضمن تطبيقات DTL المعدلة ما يلي.

من الممكن إخراج مروحة أكبر نظرًا للبوابات اللاحقة التي تتمتع بمقاومة عالية مع الحالة المنطقية العالية. تتمتع هذه الدائرة بحصانة فائقة ضد الضوضاء. إن استخدام الثنائيات المتعددة بدلاً من المقاومات والمكثفات سيجعل هذه الدائرة اقتصادية للغاية ضمن شكل الدائرة المتكاملة.

بوابة NOR المنطقية للترانزستور الثنائي

تم تصميم بوابة NOR المنطقية للترانزستور الثنائي بشكل مشابه لبوابة DTL NAND مع بوابة DRL OR مع عاكس ترانزستور. يمكن تصميم دوائر DTL NOR بشكل أكثر أناقة من خلال الجمع بين محولات DTL المختلفة من خلال مخرج مشترك. بهذه الطريقة، يمكن توحيد عدة محولات للسماح بالمدخلات اللازمة لبوابة NOR.

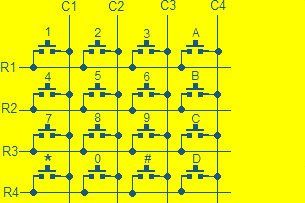

يمكن تصميم هذه الدائرة بمكونات دائرة DTL Inverter بصرف النظر عن مزود الطاقة واثنين 4.7 ك المقاومات ، 1N914 أو 1N4148 الثنائيات السيليكون. قم بتوصيل الدائرة حسب الدائرة الموضحة أدناه.

عمل

بمجرد إجراء التوصيلات، يجب توفير مصدر الطاقة للدائرة. بعد ذلك، قم بتطبيق أربع مجموعات إدخال ممكنة عند A وB من مصدر الطاقة باستخدام مفتاح الانحدار. الآن، بالنسبة لكل مجموعة إدخال، تحتاج إلى تدوين الحالة المنطقية للمخرج 'Q' كما هو موضح بـ قاد & سجل هذا الإخراج. قارن النتائج مع عملية بوابة NOR. بمجرد الانتهاء من ملاحظاتك، قم بإيقاف تشغيل مصدر الطاقة.

|

أ |

ب |

ص = (أ + ب)' |

|

0 |

0 | 1 |

|

0 |

1 | 0 |

| 1 | 0 |

0 |

| 1 | 1 |

0 |

منطق وبوابة ترانزستور الصمام الثنائي

يظهر منطق وبوابة ترانزستور الصمام الثنائي أدناه. في هذه الدائرة، المنطق يقول: يتم أخذ 1 و0 كمنطق إيجابي +5V و0V على التوالي.

عندما يكون أي دخل من A1 أو A2 (أو) A3 في حالة منطقية منخفضة، فإن الصمام الثنائي المتصل بهذا الإدخال سيكون في انحياز أمامي بعد ذلك، وسوف ينقطع الترانزستور وسيكون الخرج منخفضًا أو المنطق 0 وبالمثل، إذا كانت جميع المدخلات الثلاثة في المنطق 1، فلن يكون أي من الثنائيات موصلاً والترانزستور موصلاً بشكل كبير. بعد ذلك، يشبع الترانزستور وسيكون الخرج عالي أو منطقي 1.

يظهر أدناه جدول الحقيقة لمنطق وبوابة ترانزستور الصمام الثنائي.

|

أ1 |

A2 | A3 |

ص = أ.ب |

|

0 |

0 | 0 | 0 |

|

0 |

0 | 1 | 0 |

|

0 |

1 | 0 |

0 |

| 0 | 1 | 1 |

0 |

|

1 |

0 | 0 | 0 |

|

1 |

0 | 1 |

0 |

| 1 | 1 | 0 |

0 |

| 1 | 1 | 1 |

1 |

مقارنة بين DTL وTTL وRTL

تتم مناقشة الاختلافات بين DTL وTTL وRTL أدناه.

| دي تي ال | TTL |

من اليمين إلى اليسار |

| يشير مصطلح DTL إلى منطق الترانزستور الثنائي. | يشير مصطلح TTL إلى منطق الترانزستور-الترانزستور. | يشير مصطلح RTL إلى منطق المقاوم والترانزستور. |

| في DTL، تم تصميم البوابات المنطقية باستخدام الثنائيات والترانزستورات PN. | في TTL، تم تصميم البوابات المنطقية باستخدام BJTs.

|

في RTL، تم تصميم البوابات المنطقية باستخدام المقاوم والترانزستور. |

| في DTL، يتم استخدام الثنائيات كمكونات i/p وتستخدم الترانزستورات كمكونات o/p. | في TTL، يتم استخدام ترانزستور واحد للتضخيم بينما يتم استخدام ترانزستور آخر لأغراض التبديل. | يتم استخدام المقاوم في RTL كمكون i/p ويستخدم الترانزستور كمكون o/p |

| استجابة DTL أفضل مقارنة بـ RTL. | استجابة TTL أفضل بكثير من DTL وRTL. | استجابة RTL بطيئة. |

| فقدان الطاقة منخفض. | لديها فقدان طاقة منخفض جدًا. | فقدان الطاقة مرتفع. |

| بنائه معقد. | بنائه بسيط جدا. | بنائه بسيط. |

| الحد الأدنى لمروحة DTL هو 8. | الحد الأدنى لمروحة TTL هو 10. | الحد الأدنى لمروحة RTL هو 5. |

| عادةً ما يتراوح تبديد الطاقة لكل بوابة من 8 إلى 12 ميجاوات. | عادةً ما يتراوح تبديد الطاقة لكل بوابة من 12 إلى 22 ميجاوات. | عادة ما يكون تبديد الطاقة لكل بوابة 12 ميجاوات. |

| مناعة الضوضاء جيدة. | مناعة الضوضاء جيدة جدًا. | مناعتها للضوضاء متوسطة. |

| ويبلغ تأخير الانتشار النموذجي للبوابة 30 ns. | ويتراوح تأخير الانتشار النموذجي للبوابة بين 12 و6 ns. | ويبلغ تأخير الانتشار النموذجي للبوابة 12 ns. |

| معدل الساعة هو 12 إلى 30 ميجا هرتز. | معدل الساعة هو 15 إلى 60 ميجا هرتز. | معدل الساعة هو 8 ميجا هرتز. |

| لديها عدد كبير إلى حد ما من الوظائف. | لديها عدد كبير جدا من الوظائف. | لديها عدد كبير من الوظائف. |

| يتم استخدام منطق DTL في التبديل الأساسي والدوائر الرقمية. | يستخدم منطق TTL في الدوائر الرقمية الحديثة والدوائر المتكاملة. | يتم استخدام RTL داخل أجهزة الكمبيوتر القديمة. |

مزايا

تشمل مزايا الدائرة المنطقية للترانزستور الثنائي ما يلي.

- سرعة تحويل DTL أسرع مقارنة بـ RTL.

- إن استخدام الثنائيات داخل دوائر DTL يجعلها أرخص لأن تصنيع الثنائيات على الدوائر المتكاملة أبسط مقارنة بالمقاومات والمكثفات.

- فقدان الطاقة داخل دوائر DTL منخفض جدًا.

- تتمتع دوائر DTL بسرعات تحويل أسرع.

- يتمتع DTL بمروحة أكبر وهامش ضوضاء محسّن.

ال عيوب الدوائر المنطقية للترانزستور الثنائي تشمل ما يلي.

- تتمتع DTL بسرعة تشغيل منخفضة مقارنة بـ TTL.

- لديها تأخير كبير للغاية في انتشار البوابة.

- للحصول على مدخلات عالية، يذهب إخراج DTL إلى التشبع.

- يولد الحرارة طوال العملية.

التطبيقات

ال تطبيقات منطق الترانزستور الثنائي تشمل ما يلي.

- يستخدم منطق الترانزستور الثنائي لتصميم وتصنيع الدوائر الرقمية حيث بوابات المنطق، بوابات منطقية استخدم الثنائيات في مرحلة الإدخال وBJTs في مرحلة الإخراج.

- DTL هو نوع محدد من الدوائر المستخدمة في الإلكترونيات الرقمية الحالية لمعالجة الإشارات الكهربائية.

- يتم استخدام DTL لإنشاء دوائر منطقية بسيطة.

هكذا هذا لمحة عامة عن منطق الترانزستور ديود الدائرة، العمل، المزايا، العيوب، والتطبيقات. تعد دوائر DTL أكثر تعقيدًا مقارنة بدوائر RTL، لكن هذا المنطق قد غيّر RTL بسبب قدرتها الفائقة على FAN OUT وهامش الضوضاء المحسن، لكن DTL لها سرعة بطيئة. وهنا سؤال لك، ما هو RTL؟