في حياتنا اليومية ، نصادف أنواعًا مختلفة من الأدوات الإلكترونية. إحدى التقنيات التي أحدثت ثورة في إنتاج الإلكترونيات هي ' دارة متكاملة '. قللت هذه التقنية من حجم المنتجات الإلكترونية عن طريق زيادة كثافة بوابات المنطق، بوابات منطقية لكل شريحة. اليوم لدينا أنواع وتكوينات مختلفة من IC. كما نلاحظ من حولنا ، نجد أنه لا يمكن استخدام بعض الدوائر المتكاملة إلا لتطبيق معين واحد بينما يمكن إعادة برمجة بعض الدوائر المتكاملة واستخدامها في تطبيقات مختلفة. يتم تسمية هذه الأنواع من المرحلية باسم ASICs. لكن كيف يختلفون؟ كيف يمكن إعادة برمجتها؟ لماذا لا يمكن إعادة برمجة بعض المرحلية؟ قفز لتجد إجابات لهذه الأسئلة.

ما هي الدائرة المتكاملة الخاصة بالتطبيق ASIC؟

شكل ASIC الكامل هو الدوائر المتكاملة محددة التطبيقات. هذه الدوائر هي تطبيق محدد. المرحلية المصممة خصيصًا لتطبيق معين. عادة ما يتم تصميمها من مستوى الجذر بناءً على متطلبات التطبيق المعين. بعض الأساسيات أمثلة الدوائر المتكاملة الخاصة بالتطبيقات هي الرقائق المستخدمة في الألعاب ، والرقاقة المستخدمة لربط الذاكرة والمعالجات الدقيقة وما إلى ذلك ... يمكن استخدام هذه الشرائح فقط لهذا التطبيق الذي تم تصميمها من أجله. يفترض ، هذه أنواع المرحلية مفضلة فقط لتلك المنتجات ذات الإنتاج الكبير. نظرًا لأن ASICs مصممة من مستوى الجذر ، فإن لها تكلفة عالية ويوصى بها فقط للإنتاج الكبير الحجم.

الميزة الرئيسية لـ ASIC هي تقليل حجم الرقاقة حيث يتم إنشاء عدد كبير من الوحدات الوظيفية للدائرة على شريحة واحدة. يتضمن ASIC الحديث بشكل عام 32 بت معالج دقيق ، كتل الذاكرة ، دوائر الشبكة ، إلخ ... يُعرف هذا النوع من ASICs بـ النظام على رقاقة . مع التطور في تكنولوجيا التصنيع وزيادة البحث في طرق التصميم ، تم تطوير ASICs بمستويات مختلفة من التخصيص.

أنواع ASIC

يتم تصنيف ASICs بناءً على مقدار التخصيص المسموح للمبرمج بالقيام به على الشريحة.

أنواع ASICs

مخصص كامل

في هذا النوع من التصميم ، تم تصميم جميع الخلايا المنطقية خصيصًا لتطبيق معين. يجب على المصمم أن يصنع الخلايا المنطقية للدوائر بشكل خاص. يتم تخصيص جميع طبقات القناع للتوصيل البيني. لذلك لا يمكن للمبرمج تغيير التوصيلات البينية للرقاقة وأثناء البرمجة يجب أن يكون على دراية بتخطيط الدائرة.

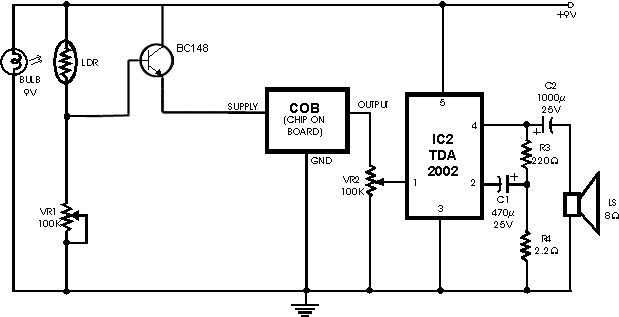

أحد أفضل الأمثلة على ASIC المخصص الكامل هو المعالج الدقيق. يسمح هذا النوع من التخصيص للمصممين ببناء دوائر تناظرية متنوعة أو خلايا ذاكرة محسّنة أو هياكل ميكانيكية على دائرة متكاملة واحدة. هذا ASIC مكلف ويستغرق وقتًا طويلاً في التصنيع والتصميم. الوقت المستغرق لتصميم هذه الدوائر المتكاملة حوالي ثمانية أسابيع.

هذه عادة ما تكون مخصصة للتطبيقات عالية المستوى. يعد الأداء الأقصى والمساحة المصغرة وأعلى درجة من المرونة من السمات الرئيسية للتصميم المخصص الكامل. في نهاية المطاف ، تكون المخاطر عالية في التصميم حيث لم يتم اختبار الخلايا المنطقية والمقاوم وما إلى ذلك ... عناصر الدائرة المستخدمة.

شبه مخصص

في هذا النوع من تصميم منطق الخلايا مأخوذة من المكتبات القياسية. لم يتم تصنيعها يدويًا كما هو الحال في التصميم المخصص الكامل. يتم تخصيص بعض الأقنعة بينما يتم أخذ بعضها من المكتبة المصممة مسبقًا. بناءً على نوع الخلايا المنطقية المأخوذة من المكتبة ومقدار التخصيص المسموح به للوصلات البينية ، يتم تقسيم ASICs إلى نوعين - ASIC المستند إلى الخلية القياسي و ASIC المستند إلى مصفوفة البوابة.

1). معيار ASIC المستند إلى الخلية

لمعرفة هذه IC أولاً ، دعنا نفهم ما تمثله مكتبة الخلية القياسية. بعض الخلايا المنطقية مثل والبوابات ، أو البوابات ، معددات ، شباشب تم تصميمها مسبقًا من قبل المصممين باستخدام تكوينات مختلفة وموحدة ومخزنة في شكل مكتبة. تُعرف هذه المجموعة بمكتبة الخلايا القياسية.

معيار ASIC المستند إلى الخلية

في الخلايا القياسية ، يتم استخدام خلايا منطق ASIC من هذه المكتبات القياسية. تتكون منطقة الخلية القياسية أو الكتلة المرنة في شريحة ASIC من خلايا قياسية مرتبة في شكل صفوف. إلى جانب هذه الكتل المرنة ، يتم استخدام الخلايا الضخمة مثل المتحكمات الدقيقة أو حتى المعالجات الدقيقة على الرقاقة. تُعرف هذه الخلايا الضخمة أيضًا بالوظائف الضخمة ووحدات الماكرو على مستوى النظام والكتل الثابتة والكتل القياسية الوظيفية.

يمثل الشكل أعلاه خلية قياسية ASIC بمنطقة خلية قياسية واحدة وأربع كتل ثابتة. يتم تخصيص طبقات القناع. هنا يمكن للمصمم وضع الخلايا القياسية في أي مكان على القالب. تُعرف أيضًا باسم C-BIC.

2). بوابة صفيف أساس ASIC

تم تحديد هذا النوع من ASIC شبه المخصص مسبقًا الترانزستورات على رقاقة السيليكون. لا يستطيع المصمم تغيير موضع الترانزستورات الموجودة على القالب. المصفوفة الأساسية هي النمط المحدد مسبقًا لمصفوفة البوابة والخلية الأساسية هي أصغر خلية متكررة في المصفوفة الأساسية.

يتحمل المصمم المسؤولية فقط عن تغيير الترابط بين الترانزستورات باستخدام الطبقات المعدنية القليلة الأولى من القالب. يختار المصمم من مكتبة مجموعة البوابة. غالبًا ما تسمى هذه بمصفوفة البوابة المقنعة. بوابة مصفوفة ASIC هي من ثلاثة أنواع. وهي عبارة عن مصفوفة بوابة القناة ، ومجموعة بوابة أقل للقناة ومجموعة بوابة منظمة.

أ). مصفوفة بوابة قناة

في هذا النوع من مصفوفة البوابة ، تُترك مسافة الأسلاك بين صفوف الترانزستورات. هذه تشبه CBIC حيث يتم ترك مساحة للتوصيل البيني بين الكتل ولكن في صفوف خلايا مصفوفة بوابة القناة ثابتة في الارتفاع بينما في CBIC يمكن تعديل هذه المساحة.

مصفوفة البوابة الموجهة

بعض السمات الرئيسية لمجموعة البوابة هذه هي- تستخدم مجموعة البوابة هذه مسافات محددة مسبقًا بين الصفوف للتوصيل البيني. وقت التصنيع من يومين إلى أسبوعين.

ب). قناة صفيف بوابة أقل

لا توجد مساحة حرة متبقية للتوجيه بين صفوف الخلايا كما هو موضح في صفيف البوابة الموجهة. هنا يتم التوجيه من أعلى خلايا مصفوفة البوابة حيث يمكننا تخصيص الاتصال بين المعدن 1 والترانزستورات. بالنسبة للتوجيه ، نترك الترانزستورات ملقاة في مسار التوجيه غير مستخدمة. مهلة التصنيع حوالي أسبوعين.

قناة مصفوفة بوابة أقل

ج). مصفوفة البوابة الهيكلية

يحتوي هذا النوع من مصفوفة البوابة على كتلة مدمجة مع صفوف مصفوفة البوابة كما هو موضح أعلاه. تتمتع مصفوفة البوابة المهيكلة بكفاءة منطقة أعلى من CBIC. مثل مصفوفة البوابة المقنعة ، فإن هذه لها تكلفة أقل وتحول أسرع. هنا يفرض الحجم الثابت للوظيفة المضمنة قيودًا على مجموعة البوابة المهيكلة. على سبيل المثال ، هل تحتوي مصفوفة البوابة هذه على منطقة محجوزة لوحدة تحكم 32 كيلو بت ولكن إذا كنا نحتاج في تطبيق ما إلى مساحة لوحدة تحكم 16 كيلو بايت فقط ، فإن المنطقة المتبقية تضيع. كلها مخصصة ربط.

مصفوفة البوابة الهيكلية

برمجة ASIC

هناك نوعان من ASICs القابلة للبرمجة. هم PLD و FPGA

PLDs (أجهزة منطقية قابلة للبرمجة)

هذه هي الخلايا القياسية المتاحة بسهولة. يمكننا برمجة PLD لتخصيص جزء من التطبيق ، بحيث يتم اعتبارهم ASIC. يمكننا استخدام طرق وبرامج مختلفة لبرمجة PLD. تحتوي هذه على مصفوفة منتظمة من الخلايا المنطقية عادةً ما تكون مصفوفة منطقية قابلة للبرمجة جنبًا إلى جنب مع flip-flops أو المزالج. توجد الوصلات هنا ككتلة واحدة كبيرة.

PROM هو مثال شائع لهذا IC. يستخدم EPROM ترانزستورات MOS كوصلة بينية لذلك من خلال تطبيق الجهد العالي يمكننا برمجته. لا تحتوي PLDs على خلايا منطقية مخصصة أو متصلة. هذه لها تحول سريع في التصميم.

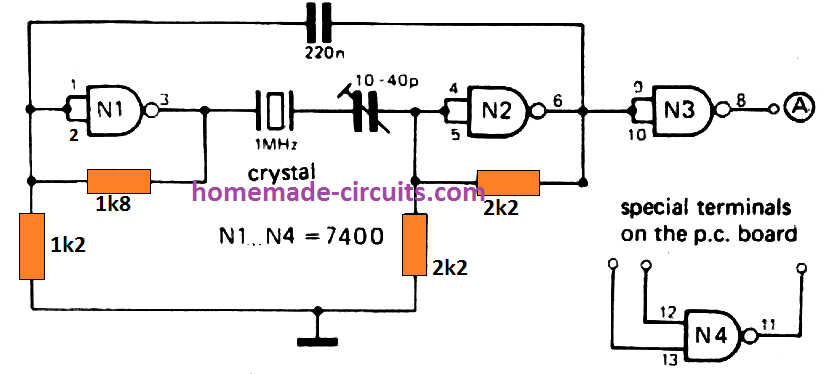

أجهزة منطقية قابلة للبرمجة

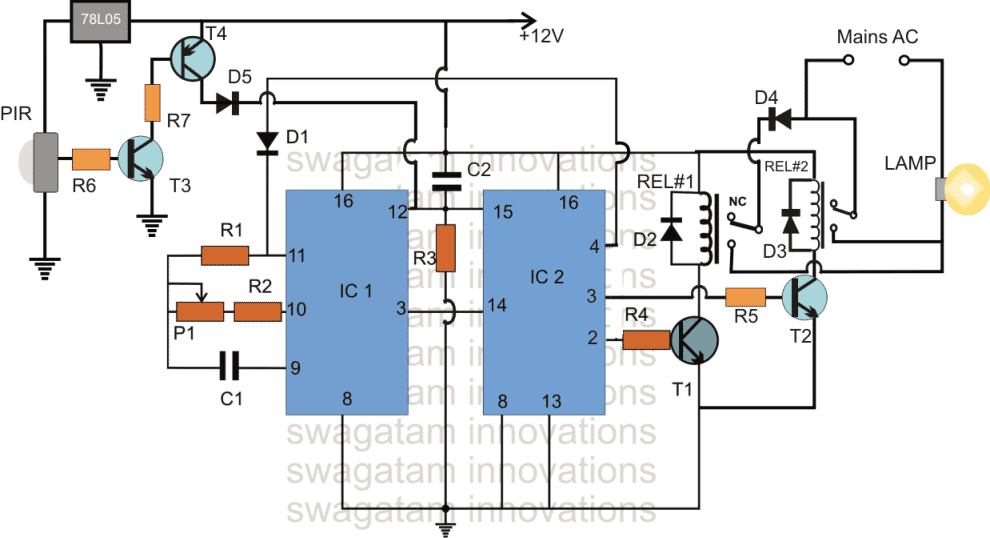

FPGAs (مصفوفة البوابة القابلة للبرمجة الميدانية)

حيث يكون لدى PLDs منطق صفيف قابل للبرمجة كخلايا منطقية FPGA لديه ترتيب يشبه مصفوفة البوابة. PLDs أصغر وأقل تعقيدًا من FPGAs. نظرًا لمرونتها وخصائصها ، يتم استبدال FPGA TTL في الأنظمة الإلكترونية الدقيقة. تحول التصميم في بضع ساعات فقط.

مصفوفة البوابة القابلة للبرمجة الميدانية

يتكون اللب من خلايا منطقية أساسية قابلة للبرمجة يمكنها أداء كليهما التوافقية و المنطق المتسلسل . يمكننا برمجة الخلايا المنطقية وربطها ببعض الطرق. الخلايا المنطقية الأساسية محاطة بمصفوفة من الوصلات البينية القابلة للبرمجة وتحيط النواة بخلايا الإدخال / الإخراج القابلة للبرمجة.

يتكون FPGA عادةً من كتل منطقية قابلة للتكوين ، وكتل إدخال / إخراج قابلة للتكوين ، ووصلات بينية قابلة للبرمجة ، ودائرة ساعة ، و ALU ، وذاكرة ، وأجهزة فك التشفير.

لقد رأينا أنواع مختلفة من ASIC المتاحة. دعنا الآن نفهم متى يتم إجراء كل هذه التخصيصات والوصلات البينية أثناء التصنيع.

تدفق تصميم الدوائر المتكاملة الخاصة بالتطبيق (ASIC)

يتم تصميم ASIC خطوة بخطوة. يُعرف ترتيب الخطوات هذا باسم تصميم أسيك تدفق. يتم عرض خطوات تدفق التصميم في مخطط التدفق أدناه.

تدفق تصميم أسيك

دخول التصميم: في هذه الخطوة ، يتم تنفيذ البنية الدقيقة للتصميم باستخدام لغات وصف الأجهزة مثل VHDL و Verilog و System Verilog.

التوليف المنطقي: في هذه الخطوة ، يتم إعداد قائمة شبكة بالخلايا المنطقية التي سيتم استخدامها وأنواع الترابط وجميع الأجزاء الأخرى المطلوبة للتطبيق باستخدام HDL.

تقسيم النظام: في هذه الخطوة ، نقسم القالب الكبير الحجم إلى قطع بحجم ASIC.

محاكاة التخطيط المسبق: في هذه الخطوة ، يتم إجراء اختبار محاكاة للتحقق مما إذا كان التصميم يحتوي على أي أخطاء.

تخطيط الأرض: في هذه الخطوة يتم ترتيب كتل netlist على الشريحة.

تحديد مستوى: في هذه الخطوة يتم تحديد موقع الخلايا داخل الكتلة.

التوجيه: في هذه الخطوة ، يتم رسم الاتصالات بين الكتل والخلايا. الاستخراج: في هذه الخطوة ، نحدد الخصائص الكهربائية مثل قيمة المقاومة وقيمة السعة للتوصيل البيني.

محاكاة ما بعد التخطيط: قبل تقديم النموذج للتصنيع ، يتم إجراء هذه المحاكاة للتحقق مما إذا كان النظام يعمل بشكل صحيح مع حمل التوصيل البيني.

أمثلة على ASIC

بعد معرفة الخصائص المختلفة لـ ASIC الآن ، دعونا نرى بعض الأمثلة على ASIC.

معيار ASIC المستند إلى الخلية: LCB 300k ، 500k من LSI Logic Company ، SIG1 ، 2 ، 3 عائلات من ABB Hafo Inc. ، GCS90K من GCS Plessey.

منتجات مصفوفة البوابة: AUA20K من Harris Semiconductor و SCX6Bxx من National Semiconductors وعائلات TGC / TEC من Texas Instruments.

منتجات PLD: عائلة PAL من Advanced Micro Devices ، عائلة GAL من Philips Semiconductors ، XC7300 و EPLD من XILINX.

منتجات FPGA: سلسلة XC2000 و XC3000 و XC4000 و XC5000 من XILINX و pASIC1 من QuickLogic و MAX5000 من Altera.

تطبيقات ASIC

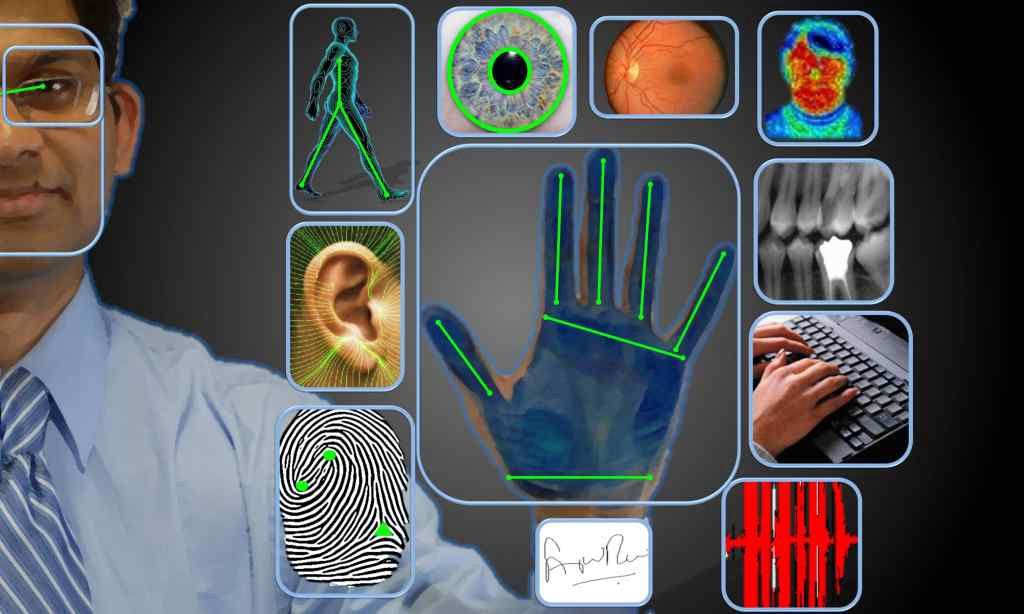

أحدث تفرد ASIC ثورة في طريقة تصنيع الإلكترونيات. قلل هذا من أحجام القالب مع زيادة كثافة بوابات المنطق، بوابات منطقية لكل شريحة. عادةً ما تُفضل ASICs للتطبيقات عالية المستوى. تستخدم شريحة ASIC كنواة IP للأقمار الصناعية وتصنيع ROM ، متحكم وأنواع مختلفة من التطبيقات في القطاعات الطبية والبحثية. أحد التطبيقات الشائعة لـ ASIC هو BITCOIN MINER.

عامل منجم البيتكوين

يتطلب تعدين العملات المشفرة طاقة أكبر وأجهزة عالية السرعة. لا يمكن لوحدة المعالجة المركزية للأغراض العامة أن توفر مثل هذه السعة الحاسوبية الأعلى بسرعة عالية. أجهزة تعدين البيتكوين ASIC عبارة عن شرائح مدمجة في اللوحات الأم المصممة خصيصًا و مزودات الطاقة ، مبنية في وحدة واحدة. إنه جهاز مصمم عن قصد وصولاً إلى مستوى الرقاقة لتعدين البيتكوين. يمكن لهذه الوحدات تنفيذ خوارزمية لعملة واحدة فقط. بالنسبة لنوع مختلف من العملات المشفرة ، من المفترض أننا نحتاج إلى عامل منجم آخر.

مزايا وعيوب ASIC

ال مزايا ASIC تشمل ما يلي.

- الحجم الصغير لـ ASIC يجعلها خيارًا عاليًا للأنظمة المعقدة الأكبر حجمًا.

- نظرًا لوجود عدد كبير من الدوائر المبنية على شريحة واحدة ، فإن هذا يتسبب في تطبيقات عالية السرعة.

- تتمتع ASIC باستهلاك منخفض للطاقة.

- نظرًا لأنها النظام الموجود على الشريحة ، فإن الدوائر موجودة جنبًا إلى جنب. لذلك ، هناك حاجة إلى الحد الأدنى من التوجيه لتوصيل الدوائر المختلفة.

- لا توجد مشكلات في التوقيت وتكوين ما بعد الإنتاج في ASIC.

ال عيوب ASIC تشمل ما يلي.

- نظرًا لأن هذه الشرائح مخصصة ، فإنها توفر مرونة منخفضة في البرمجة.

- نظرًا لأنه يجب تصميم هذه الرقائق من مستوى الجذر ، فهي ذات تكلفة عالية لكل وحدة.

- ASIC لديها وقت أكبر لهامش السوق.

ASIC مقابل FPGA

يشمل الفرق بين ASIC و FPGA ما يلي.

أسيك | FPGA |

| غير قابل للبرمجة | قابلة للبرمجة |

| مفضل للإنتاج بكميات كبيرة | مفضل للإنتاج منخفض الحجم |

| هذه خاصة بالتطبيق | تستخدم كنماذج أولية للنظام |

| تتطلب كفاءة الطاقة طاقة أقل | تتطلب كفاءة أقل للطاقة مزيدًا من الطاقة |

| هذه دوائر دائمة لا يمكن ترقيتها من وقت لآخر. | مناسب للغاية للتطبيقات التي يجب ترقية الدائرة فيها من وقت لآخر مثل رقائق الهاتف الخلوي والمحطات الأساسية وما إلى ذلك |

وبالتالي ، هذا كله يتعلق بنظرة عامة عن الدوائر المتكاملة محددة التطبيقات . تسبب اختراع ASIC في إحداث تغيير هائل في طريقة استخدام الإلكترونيات. نستخدم ASIC في حياتنا اليومية في شكل تطبيقات مختلفة. ما هي تطبيقات ASIC التي صادفتها؟ ما نوع ASIC الذي عملت معه؟